Timing Models:

If we want to perform static timing analysis on a chip using PrimeTime, every leaf cell must have a timing model. For static timing purposes, a leaf cell can be a simple macro cell (such as a NAND, NOR, or flip-flop) or a complex block (such as a RAM or microprocessor).

In Flat full chip timing analysis we need to read gate level netlist along with SPEF/SDF, timing libraries and constraints.Using this approach designers should wait till all blocks completion prior to performing full chip timing.

Hierarchical STA flow allows you to partition different blocks using timing models which Should completely model the full input/output timing characteristics without requiring the complete netlist of the block and Do not model every path in the block.

Internal register to register paths are generally discarded, as these paths can be analyzed at the block level using the complete gate-level netlist.

Hierarchical STA flow has several benefits. Hierarchical STA reduces runtime and memory usage compared to flat STA. The actual run time savings depend on the design complexity.

Types of Timing Model:

- ETM Extracted Timing Models:

- ILM Interface Logic Models

- QTM Quick Timing Model

ETM (Extracted Timing Models):

The Extracted Timing Model (ETM) is an abstraction of the block using sequential and combinational timing arcs. NLDM lookup tables are extracted for each of the timing arcs whose delay is a function of input transitions and output loads, which makes the ETM usable with different input transition times and different output loads.

Using ETMs to abstract the timing model of a complex block or IP hides the detailed design implementation information. This usage model is ideal for IP providers.

- Block based model (.lib)

- Contents of block are hidden

- Original netlist replaced by model containing timing arcs for block interfaces.

- NLDM lookup tables are extracted for each of the timing arcs.

- These arcs whose delay are a function of input transition and output load. This makes ETM usable with different input transition times and different output loads.

- Multiple modes per model

- Single PVT per model

Used for implementation (not sign-off) of IP models. Here the content are protected because the model contains abstracted timing information, without any netlist information.

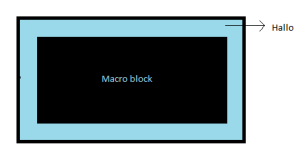

ETM model Illustration:

QTM (Quick Timing Models):

In the early stages of the design cycle, if a block does not yet have a netlist, you can use a quick timing model to describe its initial timing. Later in the cycle, you can replace each quick timing model with a netlist block to obtain more accurate timing

Interface Logic Models (ILMs):

Combinational paths from the input ports that do not encounter a sequential element and pass directly to an output port , An ILM is a partial netlist of the block that includes the boundary logic, but hides most of the internal register-to-register logic, for full-chip analysis, An interface logic model (ILM) is a partial netlist that contains only the interface logic of a block. The ILM contains :

- The combinational logic from each input port to the first stage of sequential elements of the block

- The combinational logic from the last stage of sequential elements to each output port of the block

- The clock paths to these sequential elements

- Combinational paths from the input ports that do not encounter a sequential element and pass directly to an output port

Difference between ILM and ETM :

Both ETMs and ILMs can be used in a hierarchical static analysis flow when flat analysis is not possible because of runtime and/or memory usage. An ILM offers more visibility into the netlist, which can result in easier verification, but provides less IP protection.

ETM is just like .lib means we have timing information till the pins not to the first level ( I mean to say the first gate of FF) but if we want to do timing analysis between the partition level FF to FF then we can do that with ETM.

ILM model.we can see the timing logic to the first level and vise-versa from the last level to the output pins but we can not optimize anything inside the partition.

Reference: Synopsis solvnet